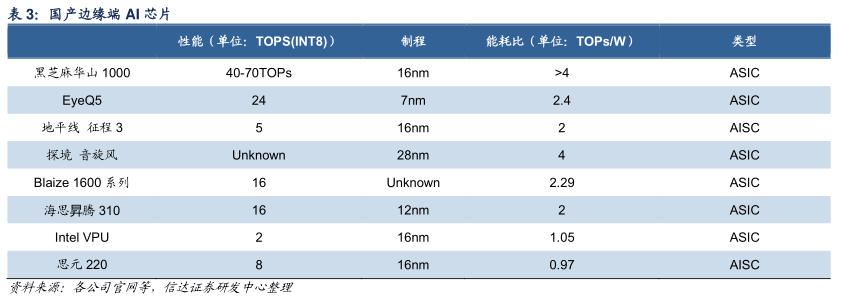

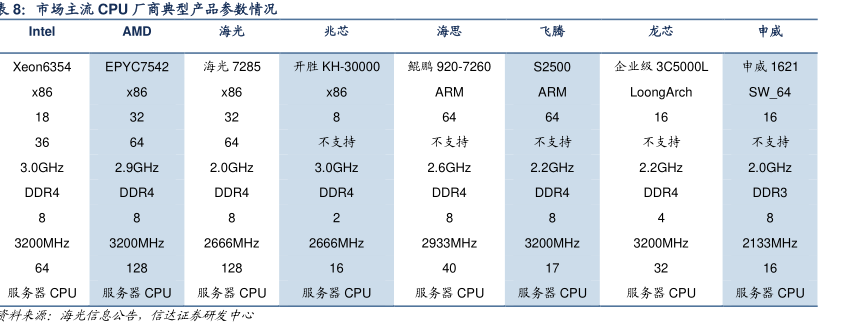

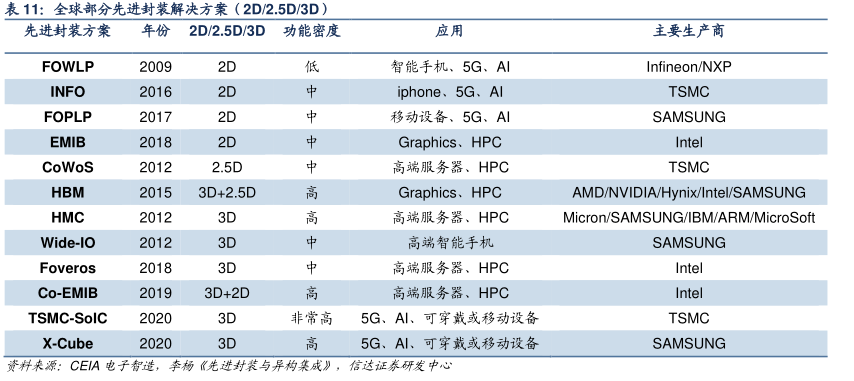

图表内容

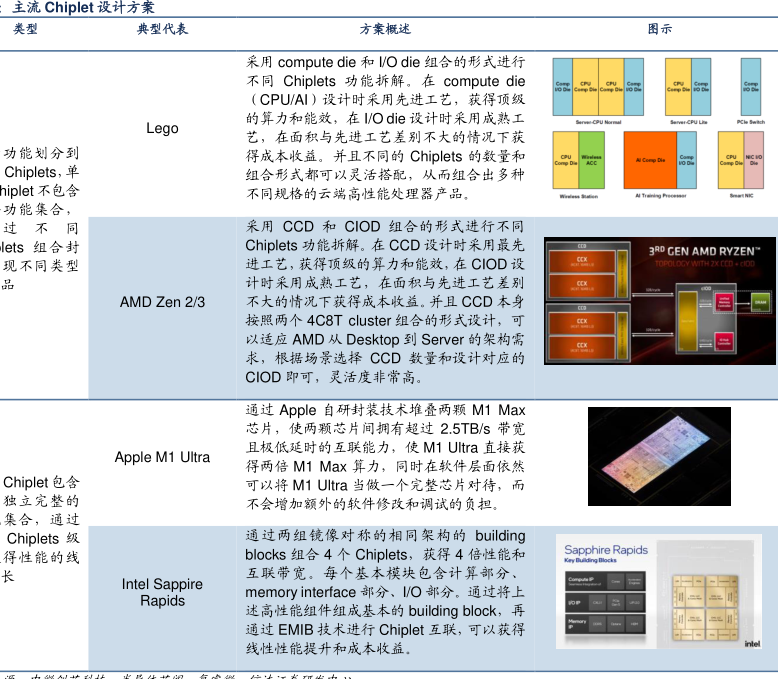

主流Chiplet设计方案

类型

典型代表

方案概述

图示

采用compute die和1/O die组合的形式进行

不同Chiplets功能拆解。在compute die

(CPU/AI)设计时采用先进工艺,获得顶级

的算力和能效,在I/Odie设计时采用成熟工

Lego

艺,在面积与先进工艺差别不大的情况下获

功能划分到

得成本收益。并且不同的Chiplets的数量和

Chiplets

单

组合形式都可以灵活搭配,从而组合出多种

niplet不包含

不同规格的云端高性能处理器产品。

功能集合,

过不同

采用CCD和CIOD组合的形式进行不同

lets组合封

Chiplets功能拆解。在CCD设计时采用最先

3RD GEN AMD RYZEN"

现不同类型

进工艺,获得顶级的算力和能效,在CIOD设

计时采用成熟工艺,在面积与先进工艺差别

AMD Zen 2/3

不大的情况下获得成本收益。并且CCD本身

按照两个4C8 T cluster组合的形式设计,可

以适应AMD从Desktop到Server的架构需

求,根据场景选择CCD数量和设计对应的

COD即可,灵活度非常高。

通过Apple自研封装技术堆叠两颗M1Max

芯片,使两颗芯片间拥有超过2.5TB/s带宽

且极低延时的互联能力,使M1 Ultra直接获

Apple M1 Ultra

得两倍M1Max算力,同时在软件层面依然

Chiplet包含

可以将M1Utra当做一个完整芯片对待,而

独立完整的

不会增加额外的软件修玫和调试的负担。

集合,通过

Chiplets级

通过两组镜像对称的相同架构的building

得性能的线

blocks组合4个Chiplets

获得4倍性能和

Sapphire Rapids

互联带宽。每个基本模块包含计算部分、

Intel Sappire

Rapids

memory interface部分、lVO部分。通过将上

述高性能组件组成基本的building block

再

通过EMIB技术进行Chiplet互联,可以获得

线性性能提升和成本收益